- #Failure to obtain a verilog simulation license how to

- #Failure to obtain a verilog simulation license verification

- #Failure to obtain a verilog simulation license code

In any project that involves doing something new to me I always have in the back of my mind, as I'm working on the design, a route to how I might test and debug the hardware.

#Failure to obtain a verilog simulation license how to

Beyond simulation is knowing how to test and debug your designs in hardware. Simulation skill improves with experience and is, to a degree, an art form.

#Failure to obtain a verilog simulation license verification

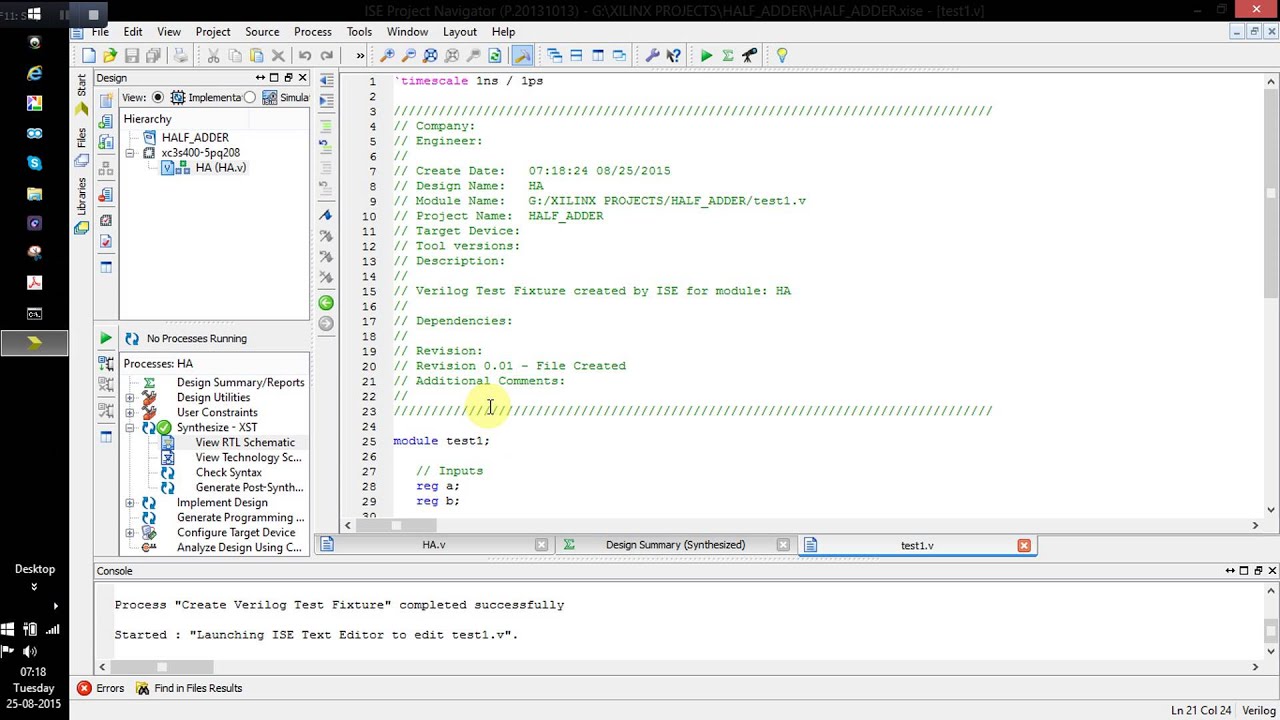

What I mean by that is that part of the design phase is the verification effort which, at a minimum, includes writing 1 or more testbenches. This may or may not be of interest, but it's my experience that jumping ahead of your knowledge and skills to do more complex designs doesn't usually work out that well. May I suggest that you start off trying to get a one clock version of your design idea working as a first step. Sometimes, this isn't a very good way to help someone get to the point where they have the knowledge to be doing what they want to do on their own.

#Failure to obtain a verilog simulation license code

Sometimes, it makes sense to answer a question by providing a follow-this-example code snippet. The Vivado-synthesis and Vivado-using-constraints references are good places to start. You should familiarize yourself with the available vendor material. I'm not trying to offend you, just nudging you toward reality,īoth Intel and Xilinx have good reference material for writing HDLs to help thier tools infer common structures like RAM, FIFO, counters, etc. The fact that you tried to implement your buffer in hardware tells me that you aren't ready to tackle this project. Once you start using multiple clocks in a design you need to understand how to write timing constraints to prevent the tools from making bad inferences about your design. You need a better understanding of how to pass data and signals between clock domains. This is especially true for structures that span multiple clock domains. Understand that there's a difference between using FPGA resources like BRAM as storage and logic LUT as storage. Unfortunately, simulation is harder to do than design so be careful about what you are reading into your simulation results. You didn't post your testbench HDL but this doesn't matter your buffer isn't even close to being able to do what you want it to do, so I can tell you that it doesn't work in simulation either.

0 kommentar(er)

0 kommentar(er)